Services de fabrication électronique à guichet unique, vous aident à réaliser facilement vos produits électroniques à partir de PCB et PCBA

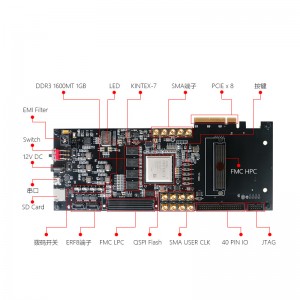

Communication par fibre optique PCIe FPGA Xilinx K7 Kintex7

- DDR3 SDRAM : 16 Go DDR3 64 bits, débit de données 1 600 Mbps

- QSPI Flash : un morceau de QSPIFLASH 128 mbit, qui peut être utilisé pour les fichiers de configuration FPGA et le stockage de données utilisateur

- Interface PCLEX8 : L'interface PCLEX8 standard permet de communiquer avec le port de communication PCIE de la carte mère de l'ordinateur. Elle prend en charge la norme PCI Express 2.0. Le débit de communication monocanal peut atteindre 5 Gbit/s.

- Port série USB UART : Un port série, connectez-vous au PC via le câble mini-USB pour effectuer une communication série

- Carte Micro SD : la carte MicroSD est complètement insérée, vous pouvez connecter la carte MicroSD standard

- Capteur de température : une puce de capteur de température LM75, qui peut surveiller la température ambiante autour de la carte de développement

- Port d'extension FMC : un FMC HPC et un FMCLPC, qui peuvent être compatibles avec diverses cartes d'extension standard

- Terminal de connexion haute vitesse ERF8 : 2 ports ERF8, qui prennent en charge la transmission de signaux à très haut débit Extension 40 broches : une interface d'E/S d'extension générale réservée avec 2,54 mm 40 broches, O effectif a 17 paires, prend en charge 3,3 V

- La connexion périphérique du niveau et le niveau 5V peuvent connecter les périphériques périphériques de différentes interfaces 1O à usage général

- Terminal SMA ; 13 têtes SMA plaquées or de haute qualité, ce qui permet aux utilisateurs de coopérer avec des cartes d'extension AD/DA FMC haute vitesse pour la collecte et le traitement du signal

- Gestion d'horloge : Source multi-horloge. Parmi celles-ci, on trouve la source d'horloge différentielle système 200 MHz SIT9102.

- Oscillateur à cristal différentiel : cristal 50 MHz et puce de gestion d'horloge programmable SI5338P : également équipée de

- EMCCLK 66 MHz. S'adapte avec précision à différentes fréquences d'horloge.

- Port JTAG : port JTAG standard 10 points 2,54 mm, pour le téléchargement et le débogage des programmes FPGA

- Puce de surveillance de tension de sous-réinitialisation : un morceau de puce de surveillance de tension ADM706R, et le bouton avec le bouton fournit un signal de réinitialisation global pour le système

- LED : 11 LED s'allument, indiquent l'alimentation de la carte, le signal config_done, FMC

- Signal indicateur d'alimentation et 4 LED utilisateur

- Clé et interrupteur : 6 touches et 4 interrupteurs sont des boutons de réinitialisation FPGA,

- Le bouton de programme B et 4 touches utilisateur sont composés. 4 interrupteurs à double course à un seul couteau

Écrivez votre message ici et envoyez-le nous

Catégories de produits

-

Téléphone

-

E-mail

-

WhatsApp

-

Skype

-

Skype

-

Skype